在數字化浪潮席卷全球的今天,電子商務已成為企業發展的核心引擎。漣影空姐范電子商務培訓,以其獨特的“空乘級”服務理念與專業嚴謹的課程體系,為企業與個人提供從技能到戰略的全方位賦能,致力于打造電商領域的精英人才與卓越管理者。

一、 體系化課程:覆蓋電商全鏈路核心崗位

漣影的培訓體系精準對應電商生態中的關鍵環節,形成了一條完整的人才培養鏈條:

- 電商總裁班:面向企業決策者與高級管理者,聚焦電商戰略規劃、商業模式創新、品牌數字化升級與資本運作。課程旨在提升領導者的宏觀視野與決策能力,引領企業在復雜市場中找準定位,實現可持續增長。

- 電商運營班:作為核心實戰課程,深入講解平臺運營規則、流量獲取與轉化、爆款打造、數據化運營及多平臺矩陣布局。學員將掌握從店鋪搭建到持續盈利的系統化運營方法論。

- 淘寶美工培訓:專注于視覺營銷領域,教授商品攝影、詳情頁設計、店鋪裝修、視頻剪輯與品牌視覺系統構建。提升學員的審美與設計執行力,以出色的視覺呈現提升產品附加值與店鋪轉化率。

- 客服培訓:將“空姐范”的高標準服務理念融入課程,培訓售前咨詢、售后問題處理、客戶關系維護、私域流量沉淀及服務團隊管理技能,旨在打造能夠極大提升客戶體驗與品牌忠誠度的專業客服團隊。

二、 特色優勢:專業、服務與實戰的結合

- “空姐范”服務標準:我們將航空服務業的高標準、精細化、注重體驗的理念植入培訓與服務全程,強調學員的學習體驗與后續的職業素養,塑造專業、優雅、高效的電商從業者形象。

- 實戰驅動教學:所有課程均以真實項目為藍本,由具備豐富一線經驗的導師帶隊,采用案例分析、模擬實操、項目復盤等形式,確保學員即學即用,快速解決實際工作中的難題。

- 電子商務運營管理服務延伸:除了培訓,漣影還為合作企業提供專業的電子商務運營管理服務,包括代運營、運營顧問、診斷優化等,將培訓成果直接轉化為企業生產力,助力企業電商業務平穩高效運行。

三、 價值呈現:賦能個人成長,驅動企業增長

對于個人學員,通過系統學習,可實現從電商小白到專業人才,乃至管理精英的跨越,提升職場競爭力與薪酬水平。

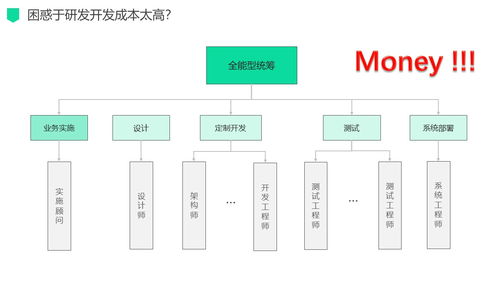

對于企業客戶,通過高管培訓、團隊技能提升或直接引入我們的運營管理服務,能夠快速構建或優化自身的電商團隊,完善運營流程,降低試錯成本,最終實現銷售業績與品牌影響力的雙重突破。

漣影空姐范電子商務培訓,不僅傳授知識與技能,更致力于傳播一種追求卓越、注重細節的職業精神。我們期待與每一位有志于電商領域的個人和企業攜手,在波瀾壯闊的數字商業時代,共馭趨勢,共贏未來。